优化PCB布局走线的静电测试整改方案

电磁兼容EMC可以分为两大类,一类是我们熟悉的辐射骚扰EMI,另一类是电磁敏感度EMS,指电子设备受电磁干扰的敏感程度,静电测试就属于EMS测试项中的一项。

1.静电测试的目的

静电测试是为了看在实际使用中产生的静电是否会对产品造成损坏或导致产品性能下降,人体静电是引起静电损失和发生意外爆炸的最主要和最经常的因素,因此国内外对电子产品的防静电危害都是要求以防人体静电为主,并建立了人体模型HBM。

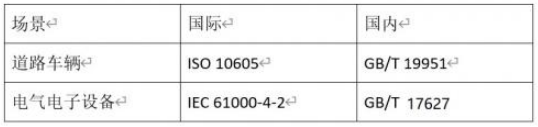

2.通用测试标准

标准中包含有标准适用的范围,术语和定义,试验等级,试验发生器,试验配置,试验程序和试验结果评价等内容,不同的产品可以参考已有标准来制定静电测试计划。

3.放电方式与等级

直接放电:直接对受试设备实施放电,包括接触放电和空气放电;

间接放电:对受试设备附近的耦合板实施放电,以模拟人员对受试设备附近的物体的放电。

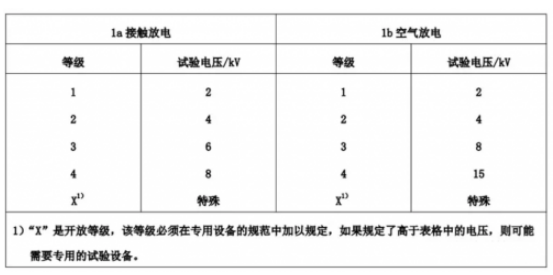

试验严酷度等级:

实验结果分类:

a) 在制造商、委托方或购买方规定的限值内性能正常

b) 功能或性能暂时丧失或降低,但在骚扰停止后能自行恢复,不需要操作者干预;

c) 功能或性能暂时丧失或降低,但需操作人员干预才能恢复;

d) 因设备硬件或软件损坏,或数据丢失而造成不能恢复的功能丧失或性能降低。

电子产品如手机,智能手表,TWS耳机在认证时往往需要做静电测试,测试过程出现不可恢复的故障,或整机复位重启。

问题详细描述

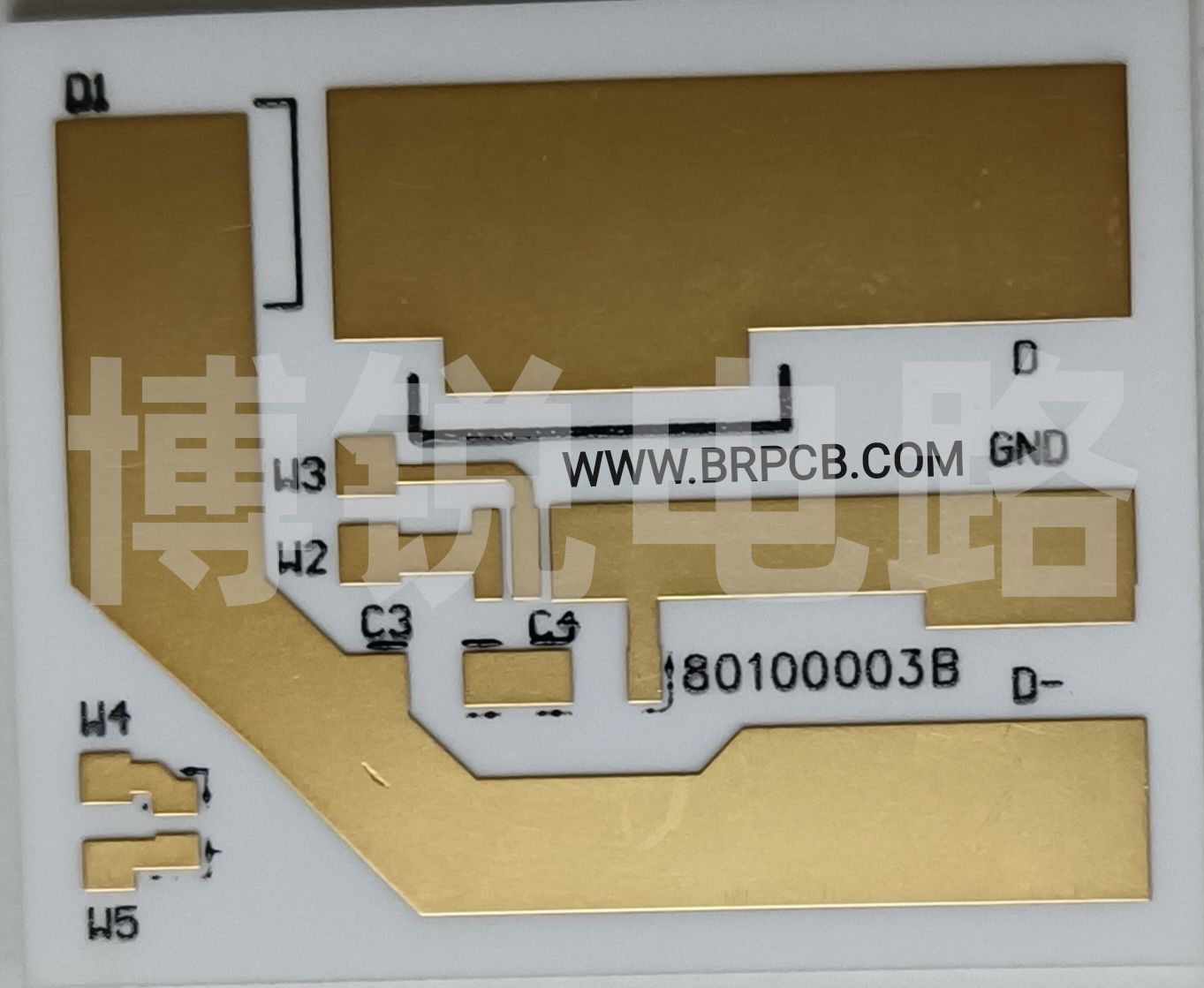

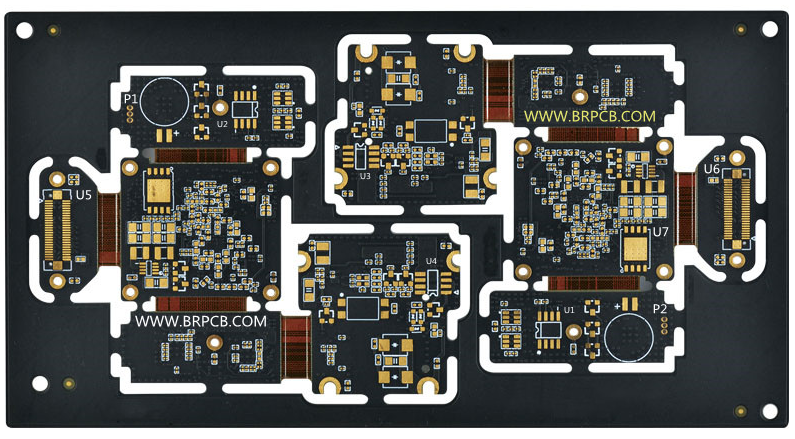

某智能手表在静电测试时,打充电输入端子的接触±4KV出现系统复位,甚至概率性卡死,长时间不能恢复。充电端子在bottom层,板子为四层一阶。

问题具体分析

1、分析如下:

经过对PCB的研究发现,在充电弹片和正极充电路径下方的相邻层信号线过多,没有完整的地来释放静电,并有高速的flash信号经过。当静电打进来时,静电瞬间干扰到信号走线,静电管还来不及释放静电,导致系统异常。

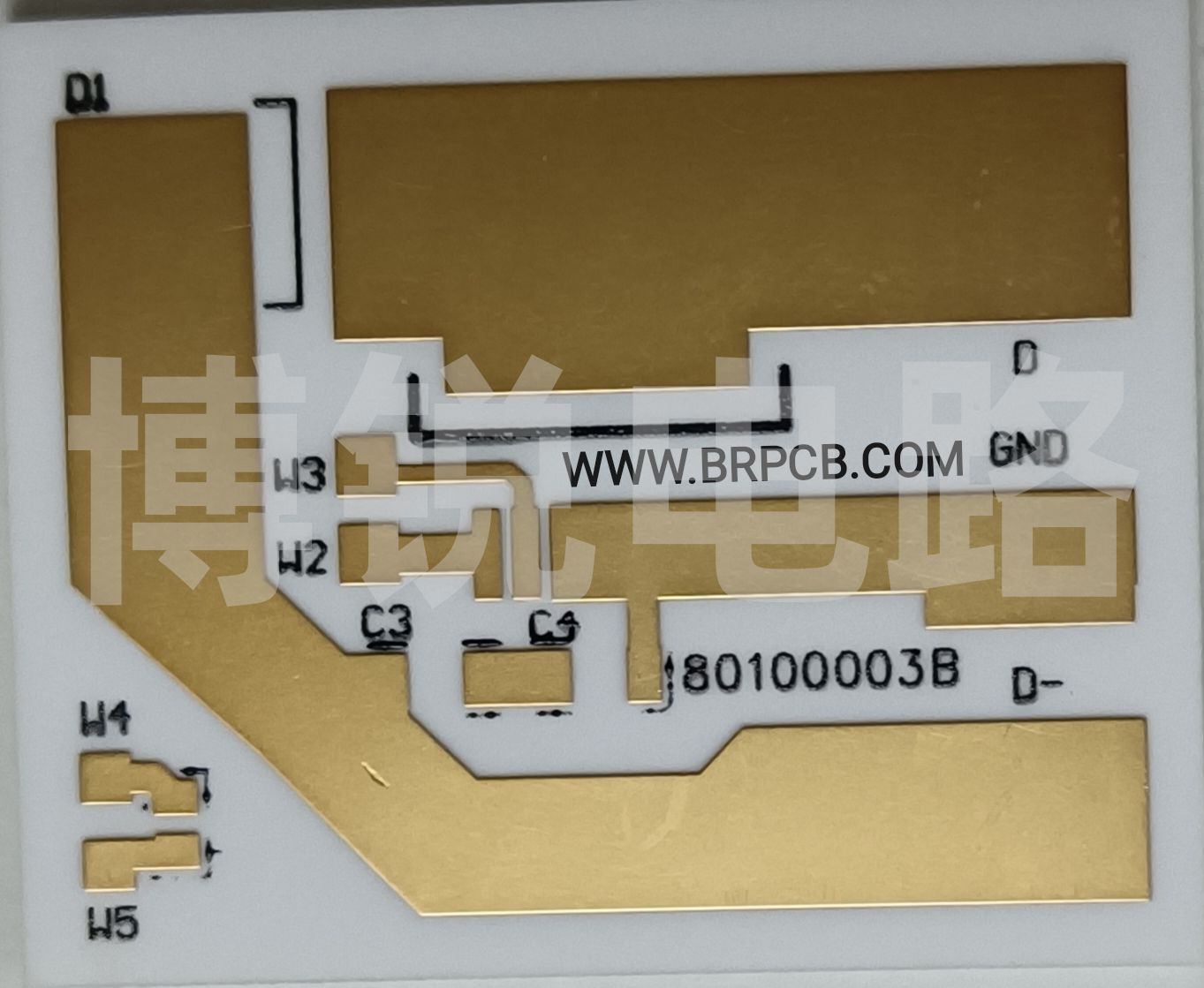

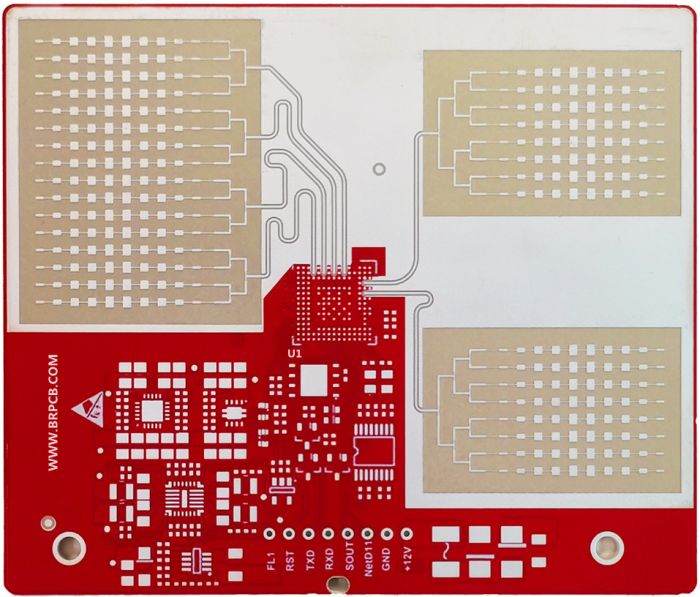

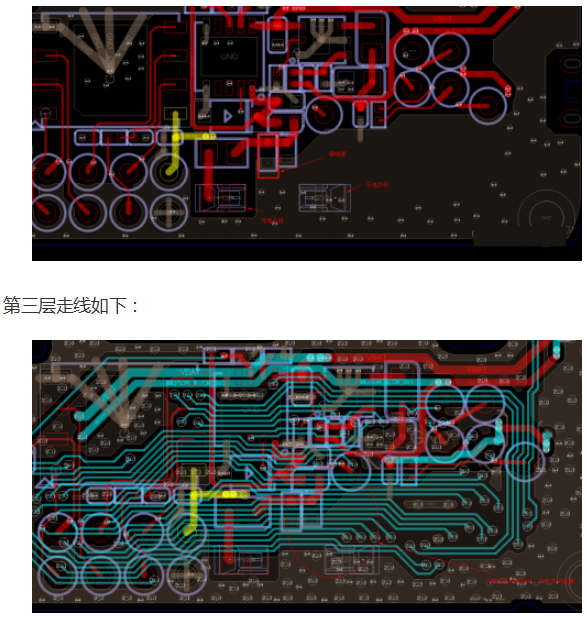

第四层(bottom层)走线如下(充电接触弹片所在层):

2、根据上面的分析做实验

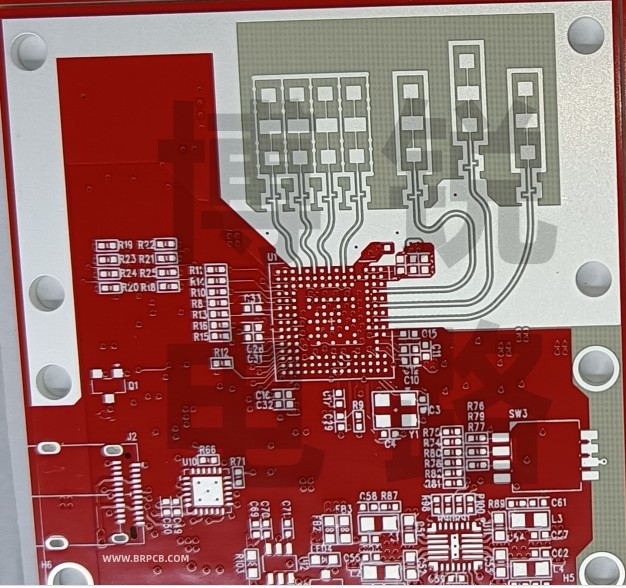

(1)在充电输入正极弹片就近并联一个静电管,让静电打正极接触弹片±6KV可以第一时间把静电从静电管处释放掉。

(2)正极弹片悬空起来(目的为了验证弹片所在的bottom层是否会影响到弹片下方相邻层的信号线),然后从充电输入正极弹片飞一根线到充电IC输入端电容处,电容之前的路径断开(确保充电通路正常),目的是为了避免原PCB上的充电路径走线有静电流过干扰到相邻的信号走线。经过这样的实验接触的±6KV稳过无异常通过。对比不处理±3KV都不行。

问题解决方案

整改思路:优化PCB布局走线(把静电路径下方信号走线移走),缩短充电回路(目的是缩短静电通过的路径),充电回路下面净空不走线,静电通过的路径邻层有完整的地。静电释放的径路是通过第三层的地进入到第二层主地层。

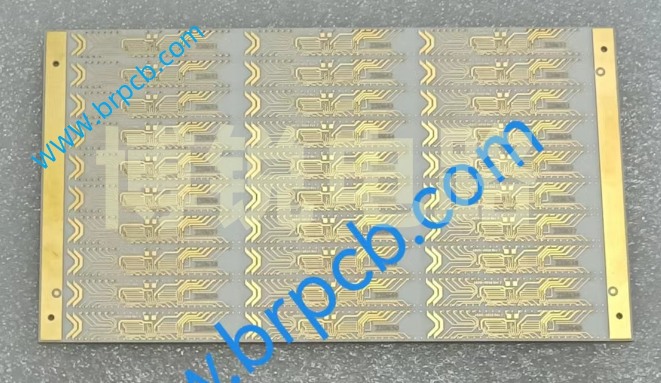

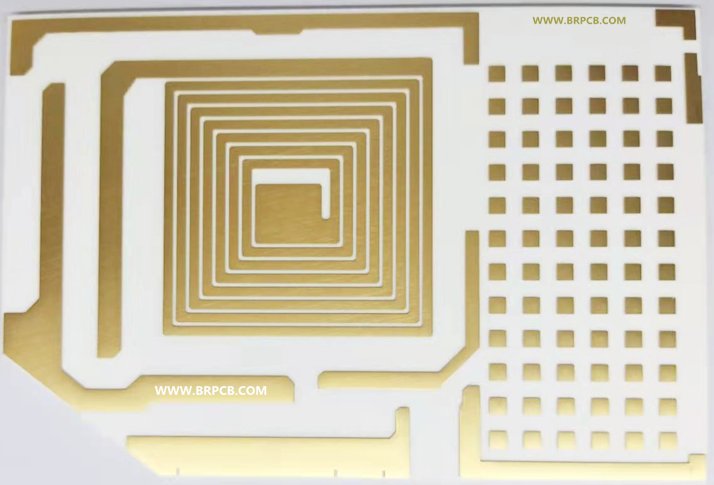

具体优化如下:

总结

静电是具有辐射干扰的,在PCB布局走线时尽可能是把静电管靠近静电进来的位置,同时要就近打孔,让静电快速进入主地层,以免干扰到其他敏感器件或走线。静电通过的路径相邻层尽可能有完整的地,避免有敏感信号经过。